Not everything in the digital world requires absolute computational precision. Many modern applications are inherently probabilistic, and their approximate calculations do not compromise the final result—in fact, they can sometimes improve it. For example, when you touch a screen, it’s not necessary to determine the touch coordinates with nanometric precision; the finger has a certain area, and a simple approximation is sufficient to efficiently identify the pressed button. Similarly, when training artificial intelligence models, the data itself is often noisy. The goal is to extract general patterns, not to perform pure mathematical calculations, so approximation in arithmetic operations does not negatively affect the final results and may even enhance the model's ability to generalize.

In this context, a research team led by Professor Li Hongji from Beihang University in China has achieved an unprecedented breakthrough. They have developed a chip that does not replace the binary system but rather extends and enriches it with a hybrid system that combines its traditional precision with the efficiency of probabilistic computing. This new chip, built on and compatible with current CMOS technologies, represents a milestone in the world of semiconductors, offering high energy efficiency without requiring modifications to the existing computational infrastructure.

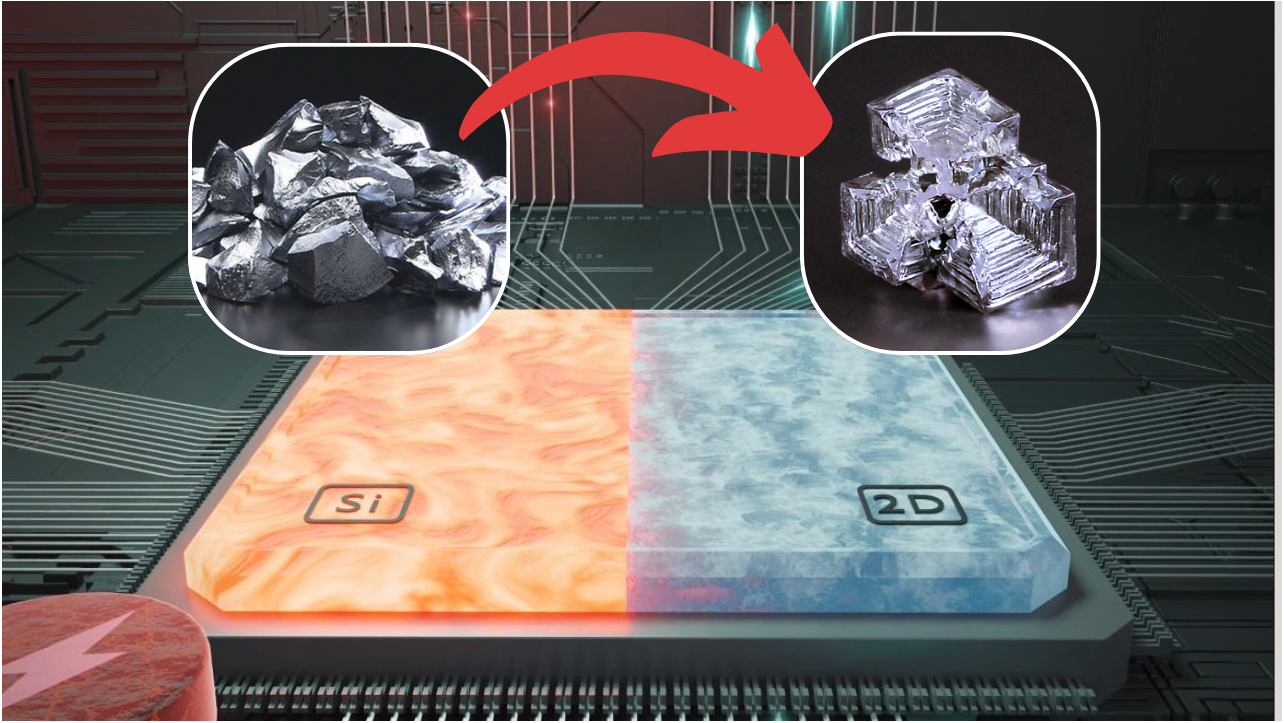

Binary computing is the foundation of all digital systems, representing data using zeros and ones, which corresponds to the on/off nature of electrical circuits. This system is effective and precise, but it requires a huge number of transistors to perform complex operations, such as those in artificial intelligence, which significantly increases power consumption. In contrast, probabilistic (or stochastic) computing represents data using streams of bits, where the proportion of "ones" reflects the desired numerical value.

To understand this more clearly: in a 4-bit binary system, the value 3 is represented as 0011. However, in a probabilistic system, this could represent the value 0.5 because the ratio of "1s" is two out of four. This representation allows operations like multiplication to be performed using a single logic gate (an AND gate), instead of a complex circuit as required in the binary system, drastically saving power and on-chip transistor count.

China Combines the Best of Both Worlds

The true achievement of the Chinese team lies not in abandoning the binary system, but in integrating it with the probabilistic system on a single chip by developing the "Hybrid Stochastic Number" concept. This intelligent approach allows the processor to leverage the advantages of both systems:

- Binary Precision: For tasks that require exact calculations where errors are not permissible.

- Probabilistic Efficiency: For tasks that tolerate approximation, such as accelerating the training of AI models or processing signals.

This hybrid chip, manufactured on a 40nm process, has proven its superiority in practical tests. In JPEG image compression applications, it efficiently reduced file sizes while maintaining perceived image quality. In training neural networks, it significantly accelerated computations with lower power consumption, making it an ideal solution for running AI models on edge devices (Edge AI).

This development represents a strategic step towards a new generation of smart and efficient computing. Instead of forcing a choice between precision and power consumption, China offers a solution that combines both. It preserves the binary system on which our digital world is built while extending it with probabilistic capabilities, opening the door to faster, more efficient, and more adaptive processors for future demands, from artificial intelligence to aerospace and autonomous vehicles.